AMD Zen 5 "Strix" APU - PerformanceDatabases.com

Release Date: 2023/08/10

Important Reminder:

Feel free to utilize content from PerformanceDatabases.com. Kindly remember to reference our site and provide a link back to this page. Thank you!

Hey everyone! Welcome to PerformanceDatabases.com. Today, we're diving into some exciting details about the upcoming AMD Zen5 Based APU.

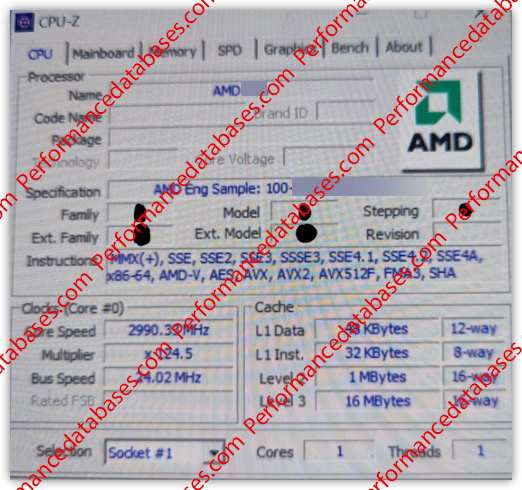

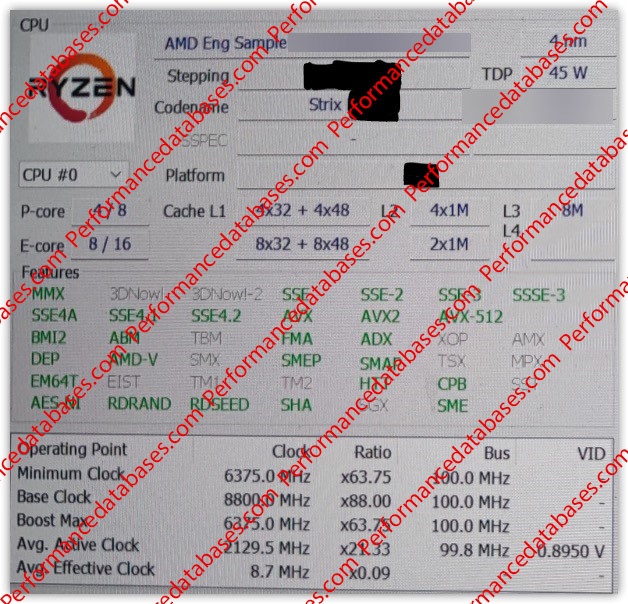

The next-gen APU, codenamed "Strix," is built on a 4nm Process and features the Big.Little CPU architecture with 4 Performance Cores and 8 Efficiency Cores. Both the P and E cores support hyper-threading. On the P Core and E Core, the L1 Data cache is 48 kb, while the L1 instruction cache is 32kb. Each P Core boasts 1Mb of cache, and with E cores, it looks like there are 4 in a group, sharing 1mb of L2 Cache. This setup is quite similar to Intel's design. Keep in mind, it's still in the ES stage, so there's more to come. We'll keep you posted on any further updates!

Disclaimer:

This website, Performancedatabases.com, serves as a platform for sharing information and data for general informational purposes only. The content presented on this website may include articles, reports, opinions, and other forms of information. It is important to note that the sources of the information provided on this website have not been verified, and their accuracy, authenticity, or reliability cannot be guaranteed.

The nature of the information shared on this website is such that it may include information obtained from various sources, including but not limited to anonymous informants, third-party contributors, and publicly available materials. The identities of these informants may be protected in order to ensure their safety and security.

Readers are advised to exercise their own judgment, critical thinking, and discretion when consuming the information presented on this website. The content here is not intended to constitute professional advice, endorsement, or factual validation. It is acknowledged that the information shared here might be speculative, unverified, or even fabricated. As such, readers are strongly encouraged to cross-reference and corroborate any information obtained from this website with reliable and authoritative sources.

Performancedatabases.com and its operators, contributors, and affiliates disclaim any responsibility or liability for the accuracy, completeness, reliability, or timeliness of the information provided on this website. Any reliance placed on the content found here is done so at the reader's own risk.

The views, opinions, and claims expressed within the content on Performancedatabases.com are solely those of the respective authors and contributors and do not necessarily reflect the views or opinions of the website's operators.

In conclusion, readers are urged to critically evaluate the information obtained from this website and to independently verify the accuracy of the information before making any decisions or taking any actions based on the content provided herein.

By accessing and using this website, you acknowledge that you have read, understood, and agreed to the terms of this disclaimer. If you do not agree with these terms, you are advised to refrain from using this website and its content.